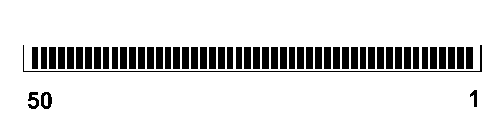

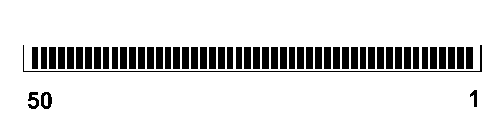

Pinout

Pinout

| NUMBER | NAME | TYPE | MODE | DESCRIPTION |

| 1 | NC | NC | - | NC |

| 2 | GND | 0V | SYSTEM | 0V |

| 3 | RESET# | INPUT | ISP | ISP RESET# signal |

| 4 | VCC | POWER | SYSTEM | Internal Mobile Equipment power source from its SIM interface (3V/5V max 10mA) |

| 5 | GND | 0V | SYSTEM | 0V |

| 6 | CLK | OUTPUT | ISP+DEBUG+USER | Clock signal |

| 7 | GND | 0V | SYSTEM | 0V |

| 8 | NC | NC | - | NC |

| 9 | NC | NC | - | NC |

| 10 | NC | NC | - | NC |

| 11 | NC | NC | - | NC |

| 12 | NC | NC | - | NC |

| 13 | NC | NC | - | NC |

| 14 | NC | NC | - | NC |

| 15 | GND | 0V | SYSTEM | 0V |

| 16 | MISO | I/O | DEBUG+USER | MMC+Debug MISO (Data INPUT) |

| 17 | MOSI | I/O | DEBUG+USER | ISP MOSI signal (Data INPUT) and MMC+Debug MOSI (Data OUTPUT) |

| 18 | SCK | I/O | ISP+DEBUG+USER | ISP SCK signal (Clock INPUT) and MMC+Debug MOSI (Clock OUTPUT) optional SPI |

| 19 | GND | 0V | SYSTEM | 0V |

| 20 | SS# | OUTPUT | DEBUG+USER | MMC+Debug Chipselect (OUTPUT) |

| 21 | PD0 | I/O | USER | GPIO/(INT0/SCL) optional Interrupt input/TWI bus CLock signal |

| 22 | PD1 | I/O | USER | GPIO/(INT1/SDA) optional Interrupt input/TWI bus Data signal |

| 23 | GND | 0V | SYSTEM | 0V |

| 24 | PF0 | I/O | USER | GPIO/ADC0 optional analog input for A/D converter |

| 25 | PF1 | I/O | USER | GPIO/ADC1 optional analog input for A/D converter |

| 26 | GND | 0V | SYSTEM | 0V |

| 27 | PG1 | I/O | USER | GPIO/RD# optional external SRAM |

| 28 | PG0 | I/O | USER | GPIO/WR# optional external SRAM |

| 29 | PC0 | I/O | USER | GPIO/A8 optional external SRAM |

| 30 | PC1 | I/O | USER | GPIO/A9 optional external SRAM |

| 31 | PC2 | I/O | USER | GPIO/A10 optional external SRAM |

| 32 | PC3 | I/O | USER | GPIO/A11 optional external SRAM |

| 33 | PC4 | I/O | USER | GPIO/A12 optional external SRAM |

| 34 | PC5 | I/O | USER | GPIO/A13 optional external SRAM |

| 35 | PC6 | I/O | USER | GPIO/A14 optional external SRAM |

| 36 | PC7 | I/O | USER | GPIO/A15 optional external SRAM |

| 37 | PG2 | I/O | USER | GPIO/ALE optional external SRAM |

| 38 | GND | 0V | SYSTEM | 0V |

| 39 | PA7 | I/O | USER | GPIO/AD7 optional external SRAM |

| 40 | PA6 | I/O | USER | GPIO/AD6 optional external SRAM |

| 41 | PA5 | I/O | USER | GPIO/AD5 optional external SRAM |

| 42 | PA4 | I/O | USER | GPIO/AD4 optional external SRAM |

| 43 | PA3 | I/O | USER | GPIO/AD3 optional external SRAM |

| 44 | PA2 | I/O | USER | GPIO/AD2 optional external SRAM |

| 45 | PA1 | I/O | USER | GPIO/AD1 optional external SRAM |

| 46 | PA0 | I/O | USER | GPIO/AD0 optional external SRAM |

| 47 | GND | 0V | SYSTEM | 0V |

| 48 | PDO | OUTPUT | ISP | ISP MISO signal (Data OUTPUT) |

| 49 | PDI | INPUT | ISP | ISP MOSI signal (Data INPUT) |

| 50 | GND | 0V | SYSTEM | 0V |

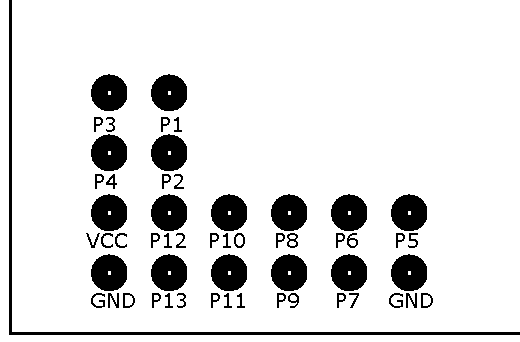

Pinout

|

Turbo Lite Pin |

ATmega128 Pin |

Function |

|

P1 |

PF2 |

ANALOG I / DIGITAL I/O |

|

P2 |

PF5 |

ANALOG I / DIGITAL I/O |

|

P3 |

PF3 |

ANALOG I / DIGITAL I/O |

|

P4 |

PF6 |

ANALOG I / DIGITAL I/O |

|

P5 |

PG1 |

DIGITAL I/O |

|

P6 |

PC2 |

DIGITAL I/O |

|

P7 |

PC1 |

DIGITAL I/O |

|

P8 |

PC6 |

DIGITAL I/O |

|

P9 |

PC4 |

DIGITAL I/O |

|

P10 |

PA7 |

DIGITAL I/O |

|

P11 |

PC7 |

DIGITAL I/O |

|

P12 |

PA4 |

DIGITAL I/O |

|

P13 |

PA6 |

DIGITAL I/O |

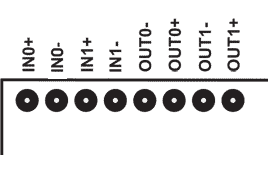

Pinout

Pinout

| Copyright © 2004-2006 BLADOX | Turbo version 1.2

|